網站建設中的網頁設計 圖片應用的藝術與策略

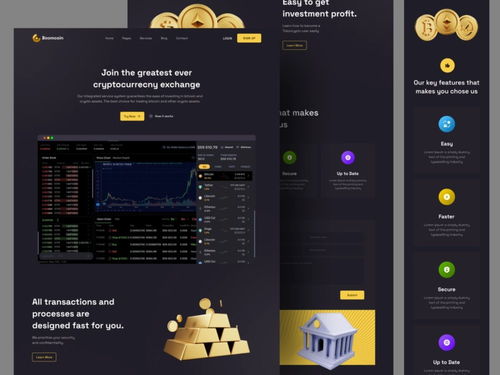

在當今數字化的時代,網站建設不僅是企業展示形象、提供服務的關鍵窗口,更是與用戶建立深度連接的重要橋梁。而網頁設計作為網站建設的核心環節,其視覺呈現直接決定了用戶的首次體驗與留存意愿。其中,圖片的應用不僅是裝飾,更是一種強大的溝通語言和信息載體。一個成功的網站,往往離不開對圖片的精心策劃、選擇與設計。

圖片在網頁設計中承擔著多重核心功能。高質量的圖片能夠迅速吸引用戶的注意力,傳遞品牌調性與專業感。例如,一個餐飲網站使用高清、誘人的美食圖片,不僅能瞬間激發訪客的食欲,更能直觀展現其菜品品質。圖片還能有效分解大段的文字信息,提升內容的可讀性與頁面的視覺節奏感。在信息過載的當下,一張恰當的配圖往往比千言萬語更具說服力。

網站建設中圖片的選擇與處理需遵循明確的設計原則。這包括:

- 相關性與一致性:所選圖片必須與網站主題、品牌定位及周邊文案高度相關,并確保整個站點的視覺風格(如色調、濾鏡、構圖)統一,以塑造連貫的品牌形象。

- 高質量與優化:使用高分辨率、清晰的圖片是基礎,但同時也需通過壓縮工具對其進行優化,以確保在不損失太多畫質的前提下,顯著提升網頁加載速度,這對移動端用戶體驗和搜索引擎排名至關重要。

- 原創性與版權:盡可能使用原創攝影、定制插畫或購買正版圖庫素材,避免侵犯版權,這既是法律要求,也是品牌專業度的體現。

- 響應式設計:確保圖片能自適應不同尺寸的屏幕(如桌面、平板、手機),不會出現變形、裁剪不當或加載過慢的問題。

圖片的布局與交互設計是提升用戶體驗的關鍵。設計師應巧妙運用網格系統、留白和視覺動線來安排圖片的位置。例如,采用卡片式設計展示產品圖集,或使用全屏大圖作為首頁背景以營造沉浸式氛圍。為圖片添加適當的交互效果,如懸停放大、懶加載、輕量級動畫等,可以增加頁面的生動感和用戶參與度,但需注意適度使用,以免影響性能或造成干擾。

從網站建設的整體流程看,圖片設計不應是后期添加的“點綴”,而應被納入前期規劃。在信息架構階段,就需考慮哪些內容適合用圖片表達;在原型設計時,規劃好圖片的占位與布局;在開發階段,與工程師協作實現圖片的技術優化。持續通過用戶反饋和數據分析(如熱圖、點擊率)來評估圖片效果,并據此迭代更新。

在網站建設中,網頁設計圖片絕非簡單的視覺填充。它是融合美學、心理學、營銷學與技術實現的綜合藝術。精心的圖片策略不僅能瞬間抓住眼球,更能高效傳遞信息、塑造品牌情感、并最終驅動用戶行為轉化。一個由優質圖片支撐的網站,無疑將在激烈的網絡競爭中脫穎而出,贏得用戶的青睞與信任。

如若轉載,請注明出處:http://www.zlstrade.com/product/45.html

更新時間:2026-02-24 21:33:27